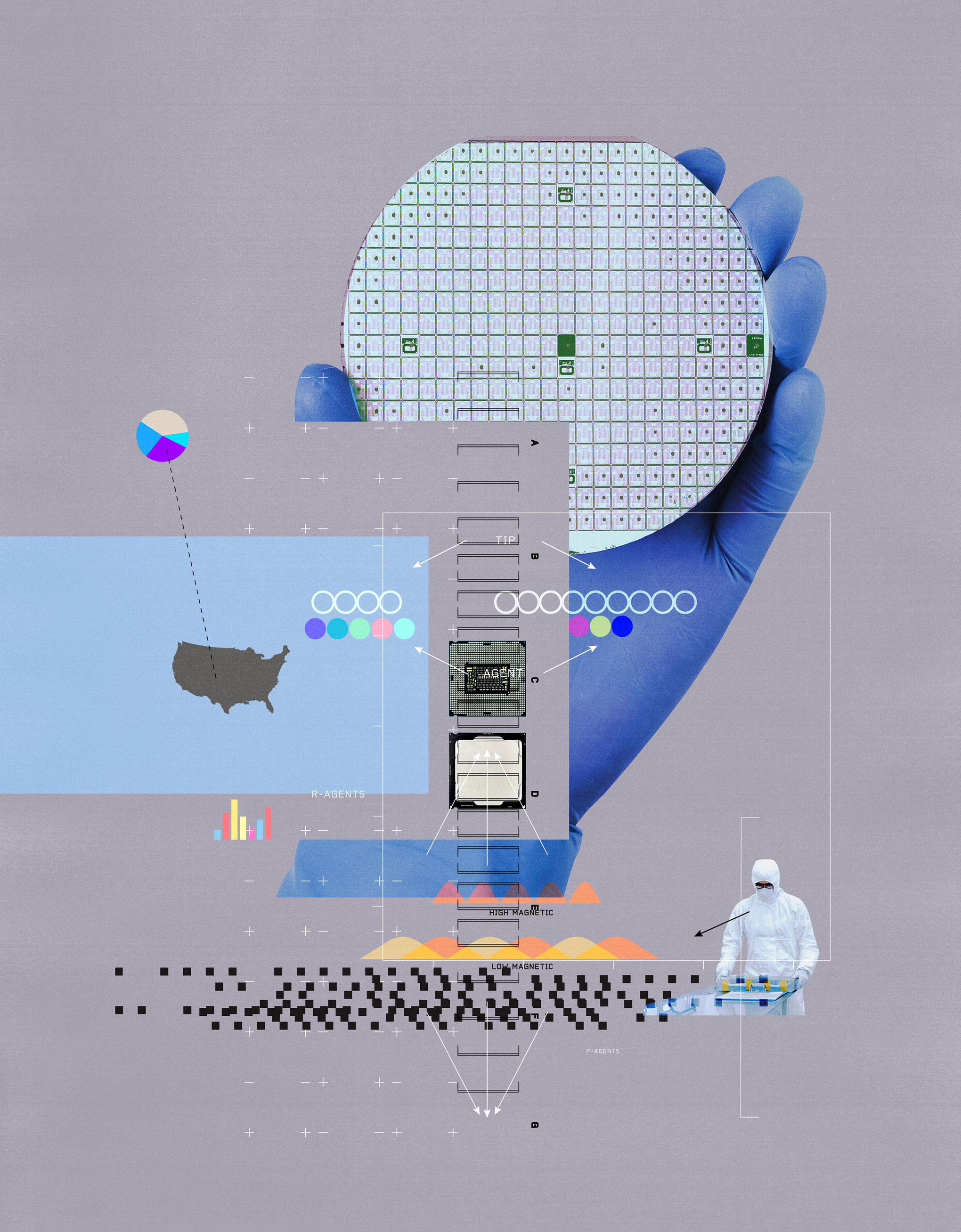

Charting a Chip Resurgence

Semiconductors are the tiny, essential heart of nearly every device we use on a daily basis—and almost none are made in the United States. Drawing on the university’s history of cross-disciplinary collaboration and traditional strength in materials science, Penn State is leading a multibillion-dollar effort to reestablish the U.S. as a leader in manufacturing the computer chips that power modern life.